# **Design Guide:**

# Designing TECs for Cost & Performance

# **Table of Contents**

| P.03 | Considerations for Designing TECs for Cost & Performance Top Considerations for Performance |

|------|---------------------------------------------------------------------------------------------|

| P.04 | About Phononic                                                                              |

| P 05 | Optimizing the Design                                                                       |

## **Considerations for Designing TECs for Cost & Performance**

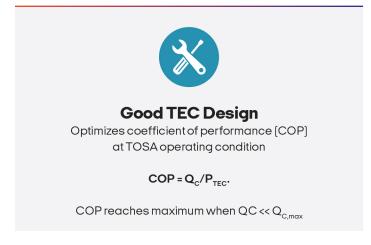

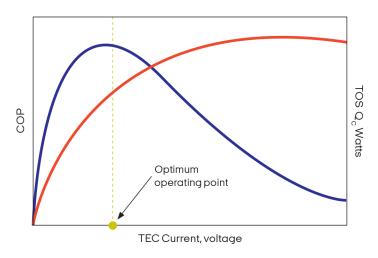

When designing a laser package, you need to maximize performance while minimizing component cost to keep your solution competitive. A major tenet of good TEC design is maximizing COP [coefficient of performance], which is the measure of a TEC's [thermoelectric cooler] heat pumping efficiency. It calculates the amount of heat removed by a TEC as compared to the amount of work required to remove it. The higher your COP, the better in-package performance you'll realize. When it comes to designing the TEC for your package, you don't have to sacrifice cost efficiency for performance – or vice versa. The ideal TEC design is optimized to deliver on both. Phononic's Applications and Design Engineers are ready to help you find the optimized design that you need.

#### **Top Considerations for Cost:**

**Au-containing solder:** Solder alloys that contain gold can provide the benefit of increasing maximum processing temperatures that the TEC can withstand, but are less cost effective. We can work with you to review your integration process temperature requirements and make recommendations for the TEC solder that strikes the best balance of cost and thermal budget.

**Use of posts:** Adding a post may streamline TEC integration, but it also adds to the overall BOM, increasing cost. If your TEC can support direct wirebonding, you can omit posts from the design and reduce cost.

Non-hermetic packages: Non-hermetic package designs are a way to reduce overall TOSA package cost and design complexity. These package types will likely replace traditional gold box packages such as box TOSAs in many applications, particularly in cooled TOSAs inside data centers. However, non-hermetic TOSA packages create their own thermal design challenges, such as managing condensation. Be aware that some approaches to non-hermetic TECs are actually "quick" fixes that can't be checked for quality, and try to cover up failure modes in non-condensing environments. This significantly degrades cooling performance and subsequently increases power consumption. Phononic's non-hermetic TEC platform actually solves the root cause of failure in condensing environments with negligible impact on performance relative to hermetic-rated TECs, and little to no efficiency loss. This enables dramatic package cost reductions without skimping on performance.

#### **Top Considerations for Performance:**

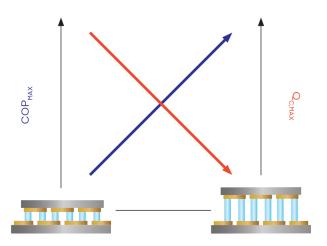

**TEC size:** TEC thickness and element layout are critical design parameters. All other things being equal, increasing

element height (thus TEC thickness) will increase the maximum achievable COP, but the maximum heat pumping capability will decrease. Therefore, thicker TECs are also not always the best choice for maximizing performance, particularly in higher heat density applications. Also, smaller TEC sizes (~3x3 mm) are often more cost effective than larger ones (~8x8 mm), so it is often beneficial to design in a smaller and thinner TEC to optimize both performance and cost effectiveness.

Heat pumping capability: This relates to the total amount of thermoelectric material within the TEC. As the cross-sectional thermoelectric element area increases, so will the heat pumping capability. That said, this can also lead to a less cost-effective TEC. However, remember that efficiency and heat pumping capacity are trade-offs with TEC thickness, which, as mentioned above, is also a key factor in cost management.

**TEC Thickness**

**Package heat density:** Heat density increases as component form factors shrink. Bear in mind that you could be looking at up to 12W or more in QSFP-DD [Quad Small Form Factor - Double Density] or OSFP [Octal Small Form Factor] optical transceiver modules.

**Package operating temperature range:** Many applications are migrating from the C-Temp (Commercial) range, which is from about 0° to 70°C, to the I-Temp (Industrial) range, which is much broader at -40° to 85°C. This trend requires TECs to perform in more demanding environments.

**Power consumption:** Transceiver power limits are being lowered industry-wide as a result of MSA specifications. TECs can be one of the biggest consumers of power within a laser package - but they are also a big opportunity to improve efficiency if you choose the right solution.

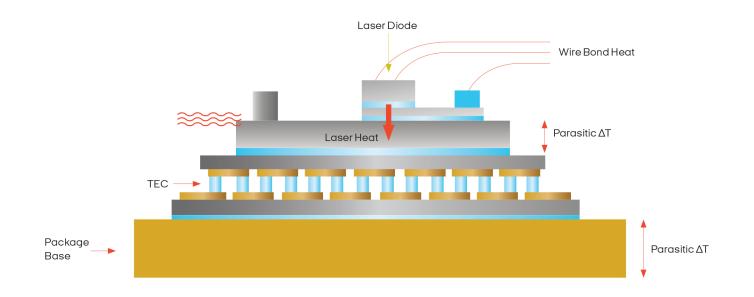

Active heat load v. total heat load: Active heat load is the input power consumed by the optical components in a TEC. Total heat load also includes any additional actives (loads from drivers or modulators) and any passive heat loads. Passive loads, which are parasitic, include heat convection or conduction through the wires that connect to the laser assembly. Heat load will increase as more wirebonds are added to an assembly, and head load

will also increase with decreased wire bond length. Wire bond heat loads can equal the active heat load, so they are a significant consideration. Proper design aims to find the balance between minimizing power consumption and increasing heat load.

**Thermal resistance:** To minimize parasitic temperature differences, good package design targets low series thermal resistance and high parallel thermal resistance. Thermal resistivity and additional temperature deltas across submounts, carriers and attachment materials such as solder or thermal epoxy must also be accounted for.

Reducing cold side thermal resistance: The TEC's cold side will always be a lower temperature than the laser diode temperature. Reducing TEC-to-laser-diode temperature deltas will reduce the TEC's power consumption. Consider using solder rather than epoxy, as solder has a lower thermal resistance. Also consider spreading resistance. Poor heat spreading from a small laser chip to the larger TEC cold side results in an increased cold side TEC temperature delta, which results in increased power consumption. The laser diode submount should be similar in size to the TEC's cold side to help improve heat spreading. Remember that thermistor-to-laser-diode offset can also change with ambient temperatures, which can affect your ability to precisely control laser wavelength.

**Reducing hot side thermal resistance:** Both hot side thermal resistance and the TEC attach material impact TEC power consumption. Solder drives higher thermal conductivity, leading to a lower temperature delta, which results in lower power consumption. Solder attach can reduce TEC power consumption by up to 20% as compared to epoxy attach. Pre-tinned solder is another design option to consider for your TEC.

| Ероху                               | Solder                         |

|-------------------------------------|--------------------------------|

| Low temperature curing              | Superior thermal conductivity  |

| Low-cost processing                 | Reworkable                     |

| Difficult to control bond thickness | Voiding can affect performance |

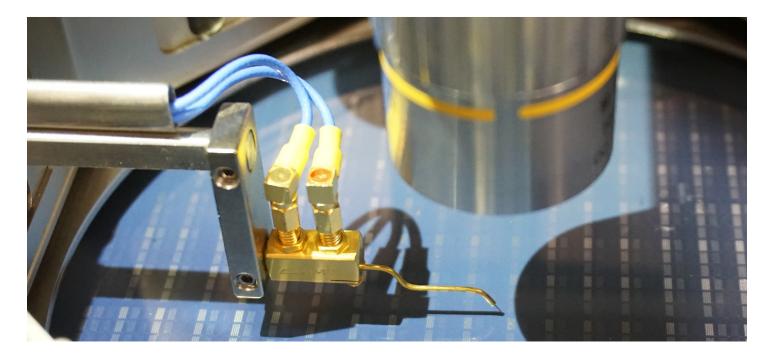

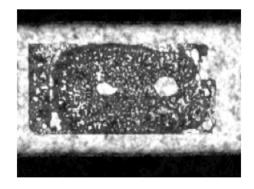

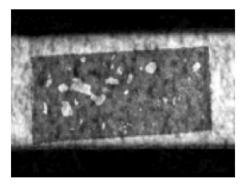

**Thermal interface processing:** Solder/epoxy type, reflow/cure temperature and process thermal budget must all be carefully designed to ensure optimized TEC performance. Characterization tools, such as X-ray or scanning acoustic microscopy, can be used as quality checks on buried interfaces. Poor, voided hot side interface such as the type shown below prevents the TEC from performing up to expectations. By comparison, a good hot side interface enables good TEC performance.

## **Hot Side Thermal Interface Characterization**

Good hot side TEC interface, leading to good TEC performance

**TEC driver:** The TEC driver can have a significant impact on TEC power consumption at the TOSA level. Remember to balance the driver efficiency roll-off that occurs at low TEC current with improved driver efficiency at higher TEC loads (TEC  $V_{op}/I_{op}$ ).

#### Optimizing the Design

The right manufacturer will carefully yet quickly converge on a TEC design that satisfies all of your design requirements while optimizing COP and reducing cost. Phononic's engineers know how to optimize for device size, parasitic temperature deltas, processing temperature range, integration options and more. They will help you identify the right BOM components so you can achieve the perfect balance of performance and part cost.

**Contact us** today to see what we can do for your application.

**Phononic** is reimagining cooling and heating in ways never thought possible. Its breakthrough solid-state technology is transforming industries and creating new markets with innovative solutions that disrupt antiquated business models and incumbent technologies. Phononic is the critical element of innovation needed to radically change what it means to be efficient, effective and sustainable. The company has been named to the 2016, 2017 and 2019 CNBC Disruptor 50 lists, received the US EPA's 2017 Emerging Tech Award, R&D 100 Award and more.